硅片——半导体行业之基石(1)

来源:中信建投

硅片——半导体行业之基石

硅片是半导体产业最重要的基础材料

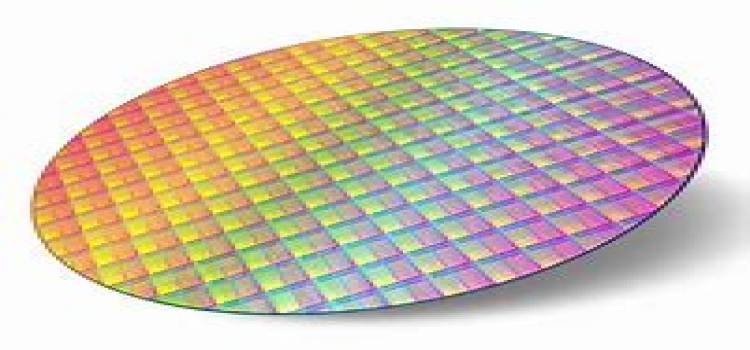

硅片是由高纯结晶硅为材料制造的圆片,一般作为集成电路和半导体器件的载体。与其他材料相比,结晶 硅的分子结构非常稳定,很少有自由电子产生,因此其导电性极低。硅基半导体材料产量大、易获取、应用广, 其应用覆盖了 90%以上的半导体产品。硅是除了氧元素之外第二丰富的元素,以多样的形式大量存在于沙子、 岩石、矿物中,相较于其他半导体材料更加易于获取。

硅片主要用于半导体和光伏两大领域,半导体硅片更值得关注。二者差异主要体现在硅片类型、纯度、平 整度、光滑度及洁净度等特性上。硅片在 IC 制造和太阳能电池领域均作为基底材料,为满足相应的电学特性, 半导体级硅晶圆都是单晶硅,而太阳能电池用的硅晶圆则单晶硅与多晶硅皆有。半导体硅片纯度标准要求为 99.999999999%以上(业内简称 11N),而光伏硅片纯度要求较低,约为 99.9999%左右。研磨、倒角、抛光、 清洗等工艺都是制作硅片的必备流程,以保证半导体大硅片表面的平整度和光滑度被控制在 1nm 以内。由于半 导体硅片制造较难、下游应用广泛、市场价值较高,因此也是硅片核心市场。

半导体硅片制造需经过一系列物理和化学操作,高纯和高精度是关键。通常将 95-99%纯度的硅称为工业硅; 纯度达 99.9999999%至 99.999999999%(9-11 个 9)的称为超纯多晶硅;在获得超纯多晶硅之后,掺入硼(P)、 磷(B)等元素改变其导电能力,放入籽晶确定晶向,制成半导体领域常用的单晶硅,切片、研磨、蚀刻、抛光、 外延(如有)、键合(如有)、清洗等步骤之后,即可制成半导体硅片。在获得单晶硅的过程中,熔体温度、 提拉速度、籽晶/石英坩埚的旋转速度以及熔体中的硼(P)、磷(B)等杂质元素浓度都起到决定性的作用。最 后,在半导体硅片上布设晶体管和多层互联线,从而制成具有特定功能的集成电路或半导体器件。

大硅片制造难度随芯片制程提高而快速提升。硅片作为基础衬底,必须具备高纯净度、平整度、清洁度和 低杂质污染度,才能完美保持芯片原本设计的功能。半导体芯片最新工艺节点已达 5nm,随着制程微缩,芯片 制造对硅片缺陷密度与缺陷尺寸的容忍度不断降低,质量控制更严格。随尺寸增加,硅片质量控制和制造难度 也倍数增加,难度主要体现在拉晶环节对速度和温度的精准把控,以及制造设备对晶圆工艺腔体均匀性的处理。

硅片正朝大尺寸和先进工艺发展,并衍生出多品类的需求结构

硅片(或硅基半导体)是目前产量最大、应用最广的半导体材料,远高于其他元素半导体或化合物半导体。常见半导体材料包括硅(Si)、锗(Ge)等元素半导体及砷化镓(GaAs)、氮化镓(GaN)等化合物半导体。 相较于锗,硅的熔点为 1415℃,高于锗的熔点 937℃,较高的熔点使硅可以广泛用于高温加工工艺;硅的禁带 宽度大于锗,更适合制作高压器件。相较于砷化镓,硅安全无毒、对环境无害,而砷元素为有毒物质;并且锗、 砷化镓均没有天然氧化物,在晶圆制造时还需要在表面沉积多层绝缘体,这会导致下游晶圆制造生产步骤增加 从而使生产成本提高。根据 SEMI 统计数据,全球 95%以上的半导体器件和 99%以上的集成电路采用硅作为衬 底材料,而化合物半导体市场占比在 5%以内。由此可见,在半导体领域,硅片占据了半导体衬底的核心地位。

单晶硅片与多晶硅片

硅片分为单晶硅和多晶硅,半导体行业使用单晶硅。根据晶胞排列是否有序,硅片可分为单晶硅和多晶硅。 二者在力学、光学与电学等物理性质上存在着差异,单晶硅的电学性质通常优于多晶硅。通常由于单晶硅的硅 片内部只由一个晶料粒构成,基本完整的结构使得其光电转换效率更高,在 18%~24%左右,而多晶硅片的光电 转换效率在 15%~19%左右。由于多晶硅片制造工艺简单、价格低廉,更高的性价比使其在硅片市场中更受下游 生产商青睐。同时,目前随着单晶硅片生产技术的进步以及规模化生产效应的影响,其成本实现了一定程度上 的降低,市场价格的下调也开始使得单晶硅片市场份额不断增加。

不同尺寸规格的硅片

可按照尺寸规格对硅片分类,硅片制造随着尺寸增大对设备和工艺的要求有所提高。以直径计算,半导体 硅片的尺寸规格主要有 50mm(2 英寸)、75mm(3 英寸)、100mm(4 英寸)、150mm(6 英寸)、200mm(8 英寸)与 300mm(12 英寸)。为了与摩尔定律同步,即集成电路上的晶体管数量每隔 18 个月提升一倍,相应 集成电路性能增强一倍,成本下降一半,芯片制造厂商需要不断改良技术,提升单个硅片可生产的芯片数量、 降低单个硅片的制造成本。而硅片尺寸越大,单个硅片上可制造的芯片数量就越多,单位芯片的成本随之降低。 因此厂商们纷纷向大尺寸硅片发展。

在摩尔定律的影响下,硅片正不断向着大尺寸方向发展。为提高生产效率并降低成本,向大尺寸演进是半 导体硅片的发展方向。硅片尺寸变大,单位芯片的成本随之降低。硅片边缘处的一些区域通常无法被利用,造 成浪费,这是因为需要在圆形硅片上制造矩形的芯片。而当硅片的尺寸变大,硅片边缘损失就会越小,芯片成 本从而降低。300mm 硅片的可使用面积超过 200mm 硅片的两倍以上,可使用率(衡量单位晶圆可生产的芯片 数量的指标)是 200mm 硅片的 2.5 倍左右。

12 英寸硅片是目前业内主流,18 寸硅片尚未成熟。根据 SEMI 统计数据,2018 年全球 12 英寸硅片出货面 积约占硅片总出货量的 63%,其次是 8 英寸,约占 26%。12 英寸硅片的下一站是 18 英寸(450mm)硅片,但 由于 12 英寸硅片可满足当前生产需求,且 18 英寸硅片设备研发难度极大,面临资金和技术双重压力。据 SEMI 估算,一个 18 英寸晶圆厂的耗资将高达 100 亿美元,远超出 12 英寸晶圆厂的投入成本,且其只能使芯片单位 面积价格下降 8%,因此晶圆厂向 18 英寸转移的速度较缓,预计到 2020 年以后 18 英寸硅片才可能初步量产。

工艺制程的不断精进也提升了对硅片的技术要求。硅片的工艺制程与尺寸并行发展,每一制程阶段与硅片 尺寸相对应,制程的提升对硅片尺寸的增大提出了要求。随着半导体芯片量产制程达到 7nm 甚至更精细,18 英 寸等更大尺寸的硅片有望在未来获得需求。具体来看两者的需求逻辑如下:

制程进步→晶体管缩小→晶体管密度成倍增加→性能提升。

晶圆尺寸增大→每片晶圆产出芯片数量更多→效率提升→成本降低。

不同用途的硅片

根据用途分类,半导体硅片可分为抛光片、退火片、外延片、结隔离片和以 SOI 硅片为代表的高端硅片。其中,抛光片是用量最大的产品,其他的硅片产品都是在抛光片的基础上二次加工产生的。

抛光片是最基础、应用范围最广的硅片。抛光片(PW-Polished Wafer)可直接用于制作半导体器件,广泛应 用于存储芯片与功率器件等,也可作为外延片、SOI 硅片等其他类型硅片的衬底材料。随着集成电路特征线宽 的不断缩小,光刻精度日益精细,硅片上极其微小的不平整都会造成集成电路图形的形变和错位,硅片制造技 术面临越来越高的要求和挑战。硅片表面颗粒度和洁净度对半导体产品的良率也有直接影响。因此,抛光工艺 对提高硅片表面的平整度和清洁度至关重要,主要原理为通过去除加工表面残留的损伤层,实现半导体硅片表 面平坦化,减小粗糙度。

退火片相较于抛光片而言,其表面的完整性更好,常用于 CMOS 元件制造以及 DRAM 制造。抛光片的缺 点随着制程技术的不断发展和工艺线宽的不断缩小而逐渐暴露出来。在此背景下,退火片(AW-Annealed Wafer) 应运而生。通过将抛光片置于充满氩气或氧气的高温环境中,按照一定的程序进行升温、降温过程,大幅减少 抛光片表面的氧气含量,得到退火片。其目的是消除氧对于硅片电阻率的影响,提高芯片良率。因此相较于普 通的抛光片,退火片表面拥有更好的晶体完整性,可满足更高的半导体蚀刻需求。退火片主要应用于一般 CMOS 元件制造以及 DRAM 制造。

外延片的表面比切割得来的抛光片更为平滑,常用于处理器芯片、图形处理器芯片等先进的逻辑制程 IC。随着应用场景不断增加,标准硅片已不能满足某些产品的要求,因此外延片(EW-Epitaxial Wafer)得以出现。外 延是通过化学气相沉积的方式在抛光面上生长一层或多层,掺杂类型、电阻率、厚度和晶格结构都符合特定要 求的新硅单晶层。外延可减少硅片中的单晶缺陷,具有更低的缺陷密度和氧含量,提高栅氧化层的完整性,改 善沟道漏电,从而提升 IC 可靠性。外延片常在通用处理器芯片、图形处理器芯片等 CMOS 电路中使用。

SOI 硅片又称绝缘体上硅,是常见先进硅材之一,主要受 5G 射频和物联网等下游应用驱动。SOI (Silicon-on-Insulator)硅片有独特的优势,可实现全介质隔离,减少硅片的寄生电容和漏电现象,消除闩锁效应。 这主要通过顶层硅和衬底之间的氧化物绝缘埋层实现。SOI 硅片适用于耐高压、耐恶劣环境、低功耗、高集成 IC。

硅片制备:直拉法 vs 区熔法

硅片的制备包括一系列物理和化学工艺步骤。概括来说,硅片的制造步骤首先由普通硅砂拉制提炼,进而 氯化并经蒸馏后制成电子级高纯度多晶硅,该步骤主流工艺为改良西门子法;再经一系列措施制成单晶硅棒, 单晶硅棒经过切片、抛光之后,便得到单晶硅圆片,也即硅片。通常意义上的晶圆制造环节包括制成高纯硅后 的“拉晶-切片-磨片-倒角-刻蚀-抛光-清洗-检测”等步骤,而不包含芯片设计、制造、封装和测试等下游环节。

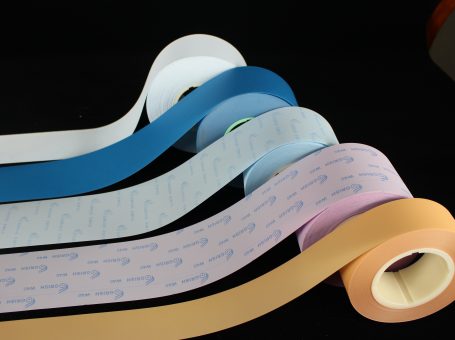

拉晶之后还需更多操作。拉晶结束后,单晶硅棒进行滚磨外径以达到较精确的尺寸,随后进行切片,获取 一定厚度的薄晶圆片,并进行倒角以增加机械强度,减少颗粒沾污。接下来进行研磨和抛光,去除硅表面损伤 层,使硅片达到微米级别的平整度并得到抛光片。抛光结束后,外延片则需要额外的外延环节,之后对抛光片 和外延片进行清洗、检测、包装出货等。SOI 硅片则在抛光片的基础上进行 Smart-cut、BESOI 或 SIMOX 工艺。

硅片制造产业链中配套材料和设备至关重要

硅片上游材料:高纯多晶硅为主要原材料,主要被美德日企业垄断

半导体硅片上游原材料主要包括电子级多晶硅、封装材料、石英坩埚、研磨轮、衬底片等,其中电子级多 晶硅(Semiconductor-Grade)为生产所需的主要原材料。

电子级多晶硅与光伏级多晶硅相比,对产品纯度、杂质控制的要求更为苛刻。多晶硅纯度需达到 99.999999999%(11N)以满足单晶硅纯度要求。虽然硅片厂商在单晶硅中添加并调整硼和磷的含量以使其具有 携带电子的特性,但当硼或磷作为杂质存在于多晶硅中时,这一含量难以控制,因此需要极高的多晶硅纯度。 制造电子级多晶硅的过程中氯硅烷的分离提纯工艺是关键步骤,而三氯氢硅除硼一直是国内电子级多晶硅材料 领域的技术瓶颈。2017 年前高纯度硅料稀缺,并被外资厂商垄断,导致国产硅片成本居高不下。包括德国瓦克、 韩国 OCI、美国 HSC、挪威 REC、日本德山、美国 SunEdison 等在内的全球几大厂商常年垄断这一技术。

中短期内,国内半导体硅片仍将依赖海外多晶硅供应。参考目前的调查结果,我们认为短期内国产电子级 多晶硅尚未具备大规模量产能力和技术水平,硅片供应目前仍需依靠几家海外多晶硅供应商。

长期看,电子级多晶硅国产化势在必行。随着 2017 年以来黄河水电、鑫华半导体、新特能源、亚洲硅业、 昆明冶研等国内厂商突破电子级高纯硅的量产制备技术,国产高纯硅正从依赖进口转向批量出口,国外大厂垄 断的局面得到缓解。我们认为国产硅片正在电子级多晶硅环节降低对外依赖度,并有望在 2021 年后实现国产化。

多晶硅价格持续下跌,多晶硅对硅片成本占比日益减小。另外我们注意到,近年来光伏级多晶硅价格持续 下跌,但高纯度多晶硅仍面临供不应求局面,部分光伏多晶硅制造商向半导体用多晶硅转移产能以扭亏为盈。 我们认为,国内厂商的迅速崛起将持续冲击国际高纯度多晶硅市场,原材料价格在硅片成本中的影响减弱。

硅片制造设备:配套设备至关重要,是硅片制造商成功的重要资源

硅片生产与制造设备关联紧密,设备厂商深度参与硅片工艺细节的制定和完善。这意味着硅片产线建设较 大程度受制于设备供给,新工艺的量产进度与之强相关;而旧工艺由于存在一定数量的二手设备和机器库存, 硅片产线投入较为顺畅。以中环领先为例,设备厂商晶盛机电斥资 5 亿参股,并与中环股份签订合作协议,使 新建产线仅用时一年半便实现投产。我们认为,只有通过与设备商保持密切合作,硅片制造商方能获得资金和 时间上的优势,因此设备在产业链中的重要性日益显现,也成为硅片制造商成功的重要资源。

大硅片制造设备长期被美德日韩等国厂商控制。其中日本企业尤为突出,在切、磨、抛设备及浆料、切削 油等材料方面占据主导地位。以上海新阳为例,其 12 英寸大硅片生产线所用的拉晶炉主要采购自韩日德,切割、 研磨、抛光设备主要采购自日本,部分非关键设备采购自韩国、台湾。相比之下,国产设备虽已覆盖各个环节, 但长久以来质量和精度与进口设备差距较大。所幸部分厂商已突破关键设备研制,国产设备采用率明显提升。

晶盛机电是国内大硅片设备龙头。公司是目前国内硅片设备产品线覆盖最齐全的供应商,硅片设备产线覆 盖率近 80%。公司和中环股份合作建立无锡大硅片项目,作为共同出资方,晶盛机电多项设备在中环的产 线得到验证;公司与硅片制造商的技术合作发挥协同效应,是国产大硅片产业链中设备领域的关键角色。

南京晶能的 CZ 单晶炉可用于 8 英寸和 12 英寸硅片生产,技术节点在国内相当靠前,单晶炉已在国内大硅 片产线上验证,实现部分国产替代。

北方华创具备单晶炉和热处理设备,是国内半导体前道设备和光伏设备龙头;目前直拉法单晶炉产品主要 用于光伏领域,具备向半导体硅片延伸的技术基础和可能性。