半导体CMP核心材料迎来国产化加速期(1)

来源:科技小酒馆

仅做知识分享,侵权联系删除!

科技创新大时代,半导体CMP核心材料迎来国产化加速期

半导体CMP材料是集成电路制造的关键制程材料

集成电路制造踏着摩尔定律的节奏快速发展,逻辑芯片的特征尺寸已发展至5nm,存储芯片堆叠层数达到128层。在这一进程中,核心材料CMP(化学机械抛光)对于集成电路制造发展起着至关重要的作用,可以说没有CMP,晶圆制程节点可能止步于0.35um。当前制造每片晶圆片,都需历经几道至几十道不等的 CMP 工艺步骤,精度要求至纳米级。

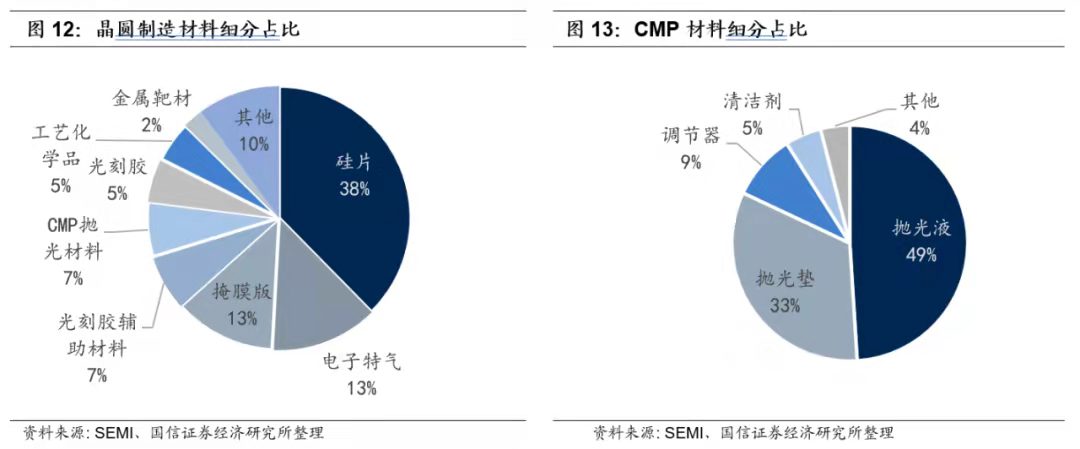

CMP材料价值量约占芯片制造成本的7%,其中抛光垫价值量约占CMP耗材的33%。由于抛光垫孔隙率、沟槽方案、硬度、刚性、可压缩性等参数对抛光质量、材料去除率和抛光批次一致性等有着显著影响,抛光垫是影响CMP效果的核心基础材料。随着集成电路制造精密度持续升级,抛光垫在CMP系统中的重要性显现持续提升。

抛光垫具有技术、专利、客户体系等较高行业壁垒。海外公司在技术积累、专利储备和产品系列上具有较强的先发优势,并且与全球主要晶圆制造厂多年合作,拥有已被验证的产品稳定性及可靠性,因此多年以来全球抛光垫市场被陶氏、Cabot等少数几家海外公司垄断约90%市场。

2020年将是国产晶圆制造企业崛起元年,随着中游制造技术能力赶超世界先进,产能有望迅速翻番增长。以中芯国际、长江存储、合肥长鑫等为代表的国内晶圆制造厂将重塑国产半导体产业链,核心材料国产化配套势在必行。根据市场预估,全球CMP市场复合增长率约6%。随着未来国内晶圆厂大幅投产,测算预计未来5年中国CMP垫市场规模增速可超10%,2023年可达约30亿元,未来可达50亿元以上。国内CMP抛光垫技术上已具备替代海外产品的能力,国产供应商即将迎来1~N的跨越式发展。

CMP是集成电路制造关键制程,抛光垫是核心耗材

1、平坦化要求日趋复杂,CMP为集成电路制造关键制程

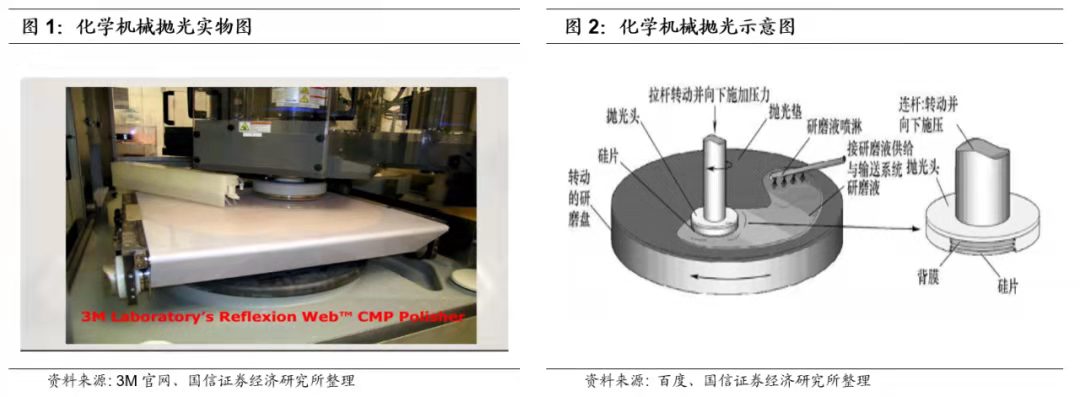

CMP全称为Chemical Mechanical Polishing,即化学机械抛光,是普通抛光技术的高端升级版本。集成电路制造过程好比建房子,每搭建一层楼层都需要让楼层足够水平齐整,才能在其上方继续搭建另一层楼,否则楼面就会高低不平,影响整体可靠性,而这个使楼层整体平整的技术在集成电路中制造中用的就是化学机械抛光技术。

CMP是通过纳米级粒子的物理研磨作用与抛光液的化学腐蚀作用的有机结合,对集成电路器件表面进行平滑处理,并使之高度平整的工艺技术。当前集成电路中主要是通过CMP工艺,对晶圆表面进行精度打磨,并可到达全局平整落差100A。~1000A。(相当于原子级10~100nm)超高平整度。而未经平坦化处理,晶片起伏随着层数增多变得更为明显,同层金属薄膜由于厚度不均导致电阻值不同,引起电致迁移造成电路短路。起伏不平的晶片表面还会使得光刻时无法准确对焦,导致线宽控制失效,严重限制了布线层数,降低集成电路的使用性能。

摩尔定律下,代工制程节点不断缩小,布线层数持续增加,CMP成为关键制程。

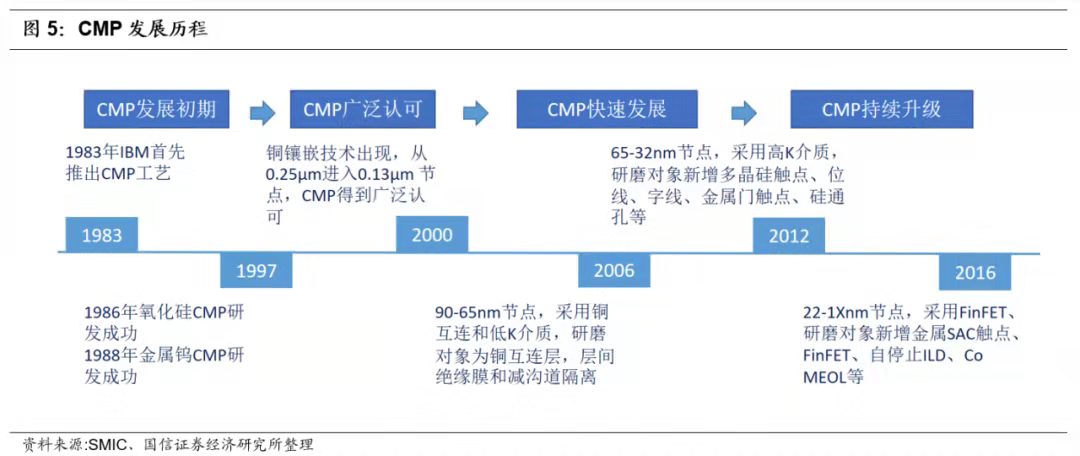

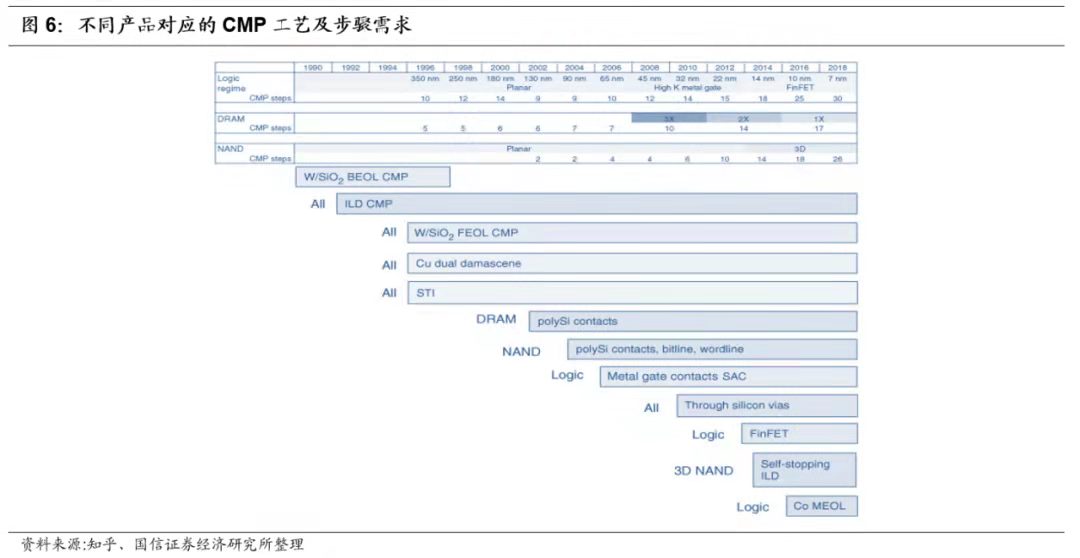

1991年IBM公司首次成功地将CMP技术应用到动态随机存储器的生产以来,随着半导体工业踏着摩尔定律的节奏快速发展,芯片的特征尺寸持续缩小,已发展至5~7nm。CMP已成功用于集成电路中的半导体晶圆表面的平面化。根据不同工艺制程和技术节点的要求,每一片晶圆在生产过程中都会经历几道甚至几十道的 CMP 抛光工艺步骤。

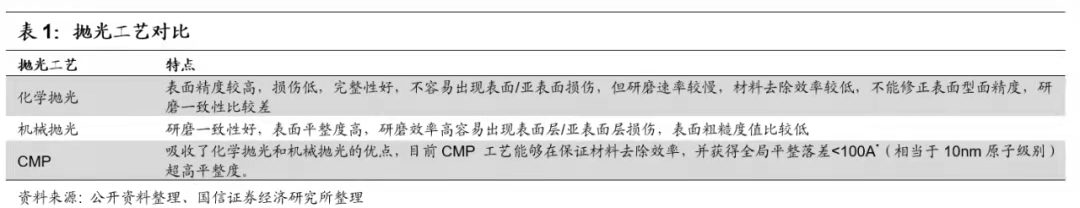

随着特征尺寸的缩小,以及布线层数增长,对晶圆平坦化精度要求不断增高,普通的化学抛光和机械抛光难以满足在当前集成电路nm级的精度要求,特别是目前对于0.35um制程及以下的器件必须进行全局平坦化,CMP 技术能够全局平坦化、去除表面缺陷、改善金属台阶覆盖及其相关可靠性,从而成为目前最有效的抛光工艺。

CMP主要运用在在单晶硅片抛光及多层布线金属互连结构工艺中的层间平坦化。集成电路制造需要在单晶硅片上执行一系列的物理和化学操作,同时随着器件特征尺寸的缩小,需要更多的生产工序,其中90nm以下的制程生产工艺均在400个工序以上。就抛光工艺而言,不同制程的产品需要不同的抛光流程,28nm制程需要12~13次CMP,进入10nm制程后CMP次数将翻倍,达到25~30次。

单晶硅片:硅片在经历拉晶、切割和研磨之后,需要进行通过化学腐蚀减薄,此时粗糙度达到10~20um左右,再进行一系列粗抛光、细抛光、精抛光等步骤,可将粗糙度控制在几十个nm以内,这样化学腐蚀减薄以及粗抛光、细抛光、精抛光等步骤,表面才可以达到集成电路的要求。单晶硅片需要2次以上的抛光,表面才可以达到集成电路的要求。

多层金属布线层:集成电路元件采用多层立体布线后,光刻工艺中对解析度和焦点深度(景深)的限制越来越高,因此需要刻蚀的每一层都需要有很高的全局平整度,即要求保证每层全局平坦化,通常要求每层的全局平整度不大于特征尺寸的2/3。12寸大硅片在加工过程中出现的非均匀效应、翘曲形变效应,使得CMP工艺在解决平坦化问题上尤为重要。多层布线条件下,任何一层导线和绝缘介质的厚度变化都会影响整颗芯片的电学稳定性,只有在CMP工艺下才能将其厚度变化控制在纳米级别范围。同时,CMP可以免除由于介质层台阶所需的过曝光、过显影、过刻蚀,在一定程度上减少了缺陷密度、提高了制程良率。

CMP平坦化工艺使用的环节包括:

氧化硅薄膜、

层间绝缘膜(ILD)、

浅沟槽隔离(STI)、

多晶硅和金属膜(如Al,Cu)等。

CMP技术最早使用在氧化硅抛光中,是用来进行层间介质(ILD)的全局平坦的,在半导体进入0.35μm节点之后,CMP更广泛地应用在金属钨、铜、多晶硅等的平坦化工艺中。随着金属布线层数的增多,需要进行CMP抛光的步骤也越多。下文举例说明集中CMP工艺的不同特点:

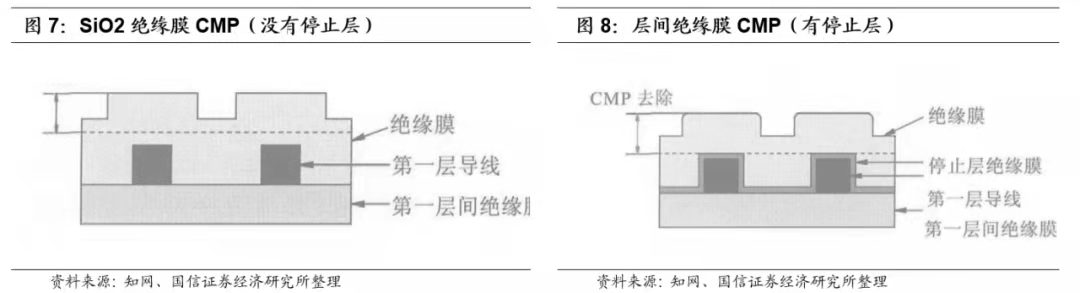

氧化硅薄膜的CMP:氧化硅多应用于做绝缘膜或隔离层,因此氧化硅层的平整度将影响往后数层的制造、导线的连接及定位的工作。通常氧化硅层多以CVD(化学汽相沉积)的方法沉积,因此会有过多的堆积层需要以CMP的方式去除,此过程没有明显的停止终点,以去除薄膜的厚度为标准,只需达到平整度要求即可。

层间绝缘膜的CMP:在层间绝缘膜的平整化方面,抛光对象有电浆辅助化学汽相沉积膜、硼磷硅玻璃及热氧化膜等。每一种对象的CMP抛光条件都随着抛光液种类、抛光压力与抛光时间而有所不同。在对不同特性的绝缘膜抛光时,大多以监测抛光终点来判定完成与否。

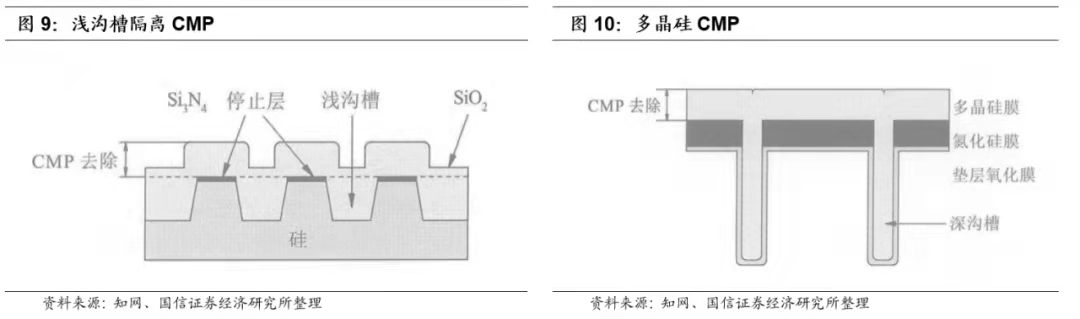

浅沟槽隔离的CMP:在硅晶片上经蚀刻形成沟槽后,利用CVD方式沉积氧化硅膜,再用CMP去除未埋入沟槽中的氧化硅膜,并以抛光速度相对缓慢的(如氮化硅膜)作为CMP的抛光停止层即终点,此时沟槽内的氧化硅即成为电路中的绝缘体膜。

多晶硅的CMP:将STI过程的沟槽加深,以CVD方式沉积氧化硅或氮化硅后,再以多晶硅作为堆积材料,用CMP去除深沟外多余的多晶硅,并以在硅晶片上及沟槽内长成的氧化硅或氮化硅膜作为CMP的抛光停止层即终点,此方法常见于沟槽电容的制造过程中。

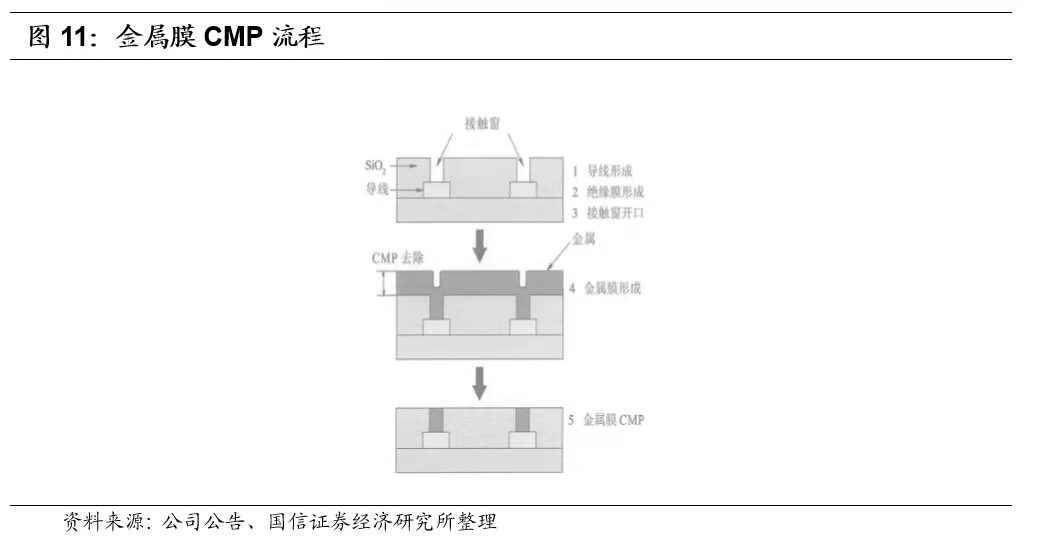

金属膜的CMP:在半导体工艺中常用作导线的金属有铝、钨、铜,CMP除了能将金属导线平整化以外,还能制作(两层电路)导线间连接的“接触窗”,即在两层电路间的绝缘膜上蚀刻出接触窗的凹槽,再以CVD方式将用作导线材料的金属沉积其中,最后再以CMP去除多余的金属层。

2、抛光垫决定CMP基础效果,重要性持续提升

CMP主要由抛光垫、抛光液、调节器等部分组成。化学机械抛光技术是化学作用和机械作用相结合的组合技术,旋转的晶圆以一定的压力压在旋转的抛光垫上,抛光液在晶圆与抛光垫之间流动,并产生化学反应。晶圆表面形成的化学反应物由漂浮在抛光液中的磨粒通过机械作用将这层氧化薄膜去除,在化学成膜和机械去膜的交替过程中实现超精密表面加工。

从价值量占比可以看到,CMP材料是芯片制造的核心耗材,占芯片制造成本约7%,其中抛光垫价值量占CMP耗材的33%左右。拆解晶圆制造成本进行,CMP材料占比较大,约为6.7%。价值量与光刻胶相近。其中抛光液和抛光垫是最核心的材料,占比分别为49%和33%。

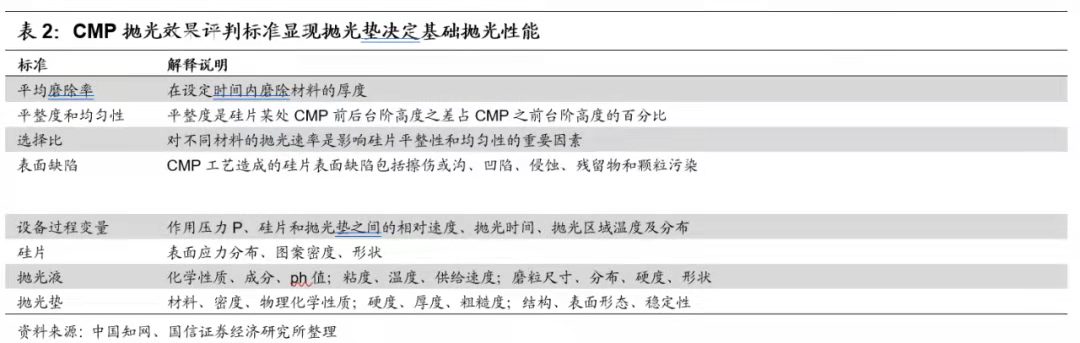

抛光垫决定了CMP工艺的基础抛光效果,并结合设备操作过程、硅片、抛光液等因素,共同影响CMP抛光结果和效率。我们一般从平均磨除率、平整度和均匀性、选择比和表面缺陷四个维度来评判抛光效果。为了更好控制抛光过程,需要详细了解CMP系统中参数所起的作用以及它们之间微妙的交互作用。其中,抛光垫的物理化学等性能在CMP工艺中发挥了重要的作用。

抛光垫的自身硬度、刚性、可压缩性等机械物理性能对抛光质量、材料去除率和抛光垫的寿命有着明显的影响。抛光垫的硬度决定了其保持形状精度的能力。采用硬质抛光垫可获得较好工件表面的平面度, 软质抛光垫可获得加工变质层和表面粗糙度都很小的抛光表面。抛光垫的可压缩性决定抛光过程抛光垫与工件表面的贴合程度, 从而影响材料去除率和表面平坦化程度。可压缩性大的抛光垫与工件的贴合面积小, 材料去除率高。

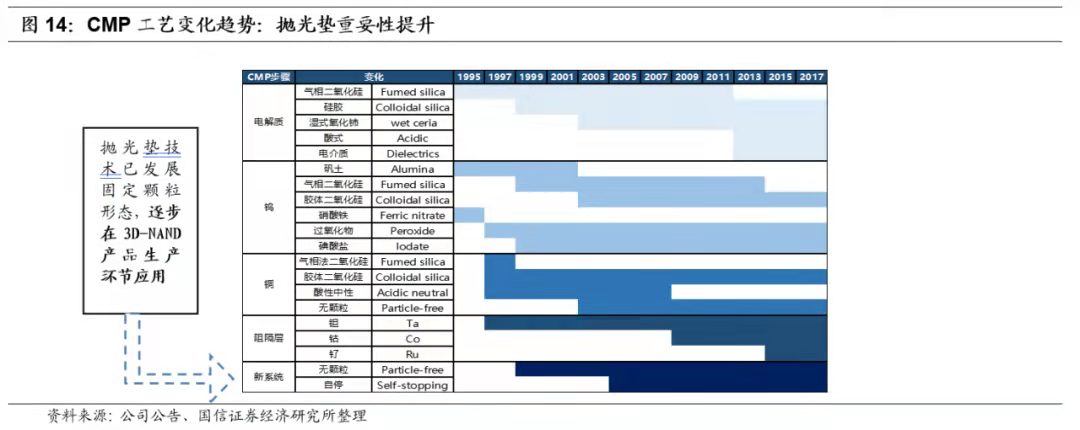

目前最新趋势,国际先进厂家在3D-Nand等更高要求的生产环节中应用固定研磨颗粒的抛光垫,其产品融合了原本存在于抛光液的抛光颗粒,显现抛光垫重要性进一步提高。